|

||||||||

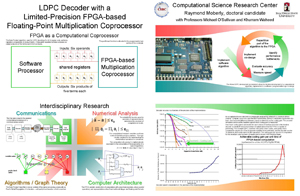

| LDPC Decoder with a Limited-Precision FPGA-based Floating-Point Multiplication LDPC Decoder with a Limited-Precision FPGA-based Floating-Point Multiplication Coprocessor | ||

|

An Implementation of the sum-product algorithm

in an FPGA considers tradeoffs between computational precision and

computational speed. The probabilistic algorithm is used for iterative

soft-decision decoding of LDPC codes. Our FPGA-based coprocessor

(design) performs computer algebra with significantly less precision

than the standard (e.g. integer, floating-point) operations of general

purpose processors with comparable iterative convergence. Using

synthesis, targeting a 3,168 LUT Xilinx FPGA, we show that key components

of a decoder are feasible and that the full single-precision decoder

could be constructed using a larger part.

Soft-decision decoding by the iterative belief propagation algorithm is impacted | ||

|

both positively and negatively by a reduction

in the precision of the computation. Reducing precision reduces

the coding gain, but the limited-precision computation can operate

faster. A proposed solution offers custom logic to perform computations

with less precision, yet uses the floating-point format to interface

with the software. Simulation results show the achievable coding

gain. Synthesis results help theorize the the full capacity and

performance of an FPGA-based coprocessor.

|

||

| • Other Abstracts • | ||