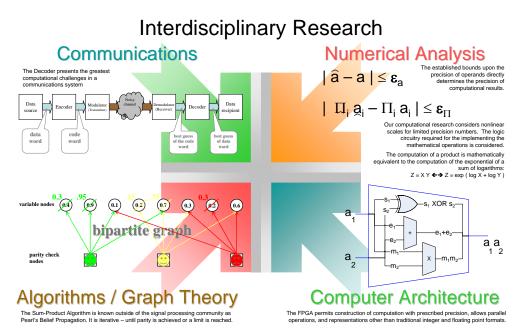

## LDPC Decoder with a Limited-Precision FPGA-based Floating-Point Multiplication Coprocessor

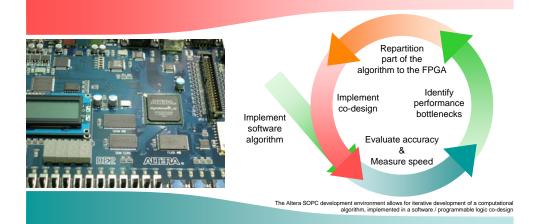

## FPGA as a Computational Coprocessor

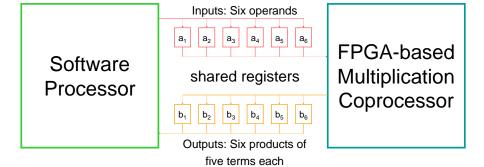

The Sum-Product algorithm, used for LDPC decoding of a (6,3)-regular code, performs repeated computations of product terms. A frequently repeated function computes six output products (of five terms each) from six inputs.

The partitioned function is allocated to the programmable logic

portion of the co-design

## **Computational Science Research Center**

Raymond Moberly, doctoral candidate with Professors Michael O'Sullivan and Khurram Waheed

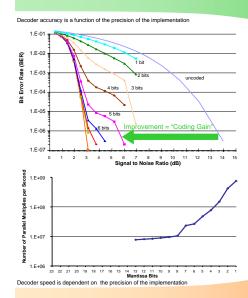

An acceptable bit error rate limit is a meaningful engineering criteria for a communications channel. Compare curves at a specified BER (where they intersect a horizontal equal-error-rate line) – the horizontal difference between curves is referred to as the *coding gain*. The uncoded simulation serves as the baseline against which coding gain is measured.

SAN DIEGO STATE

UNIVERSITY

How much coding gain is achievable for each choice of mantissa precision in the iterative decoder is a tradeoff versus the number of multiplications that the FPGA is capable of performing. The example LDPC code has 1000 parity-check nodes, each parity-check computation requires six of the 5-operand multiplies to be performed, and the decoder runs for 10 iterations; that works out to 60,000 operations. The coding gain per second of computation for this example code has been computed and is shown in the following figure. Achievable coding gain per unit time of

SUBJECT OF CONTRACT OF CONTRAC